# CFW32C7UL 应用概要

Version 1.0

2019-10

For more information, visit our website at:

# 郑重声明

本文档以及其所包含的内容为厦门码灵半导体技术有限公司所有,并受中国法律和其他可适用的国际公约的版权保护。未经码灵的事先书面授权,不得对本文档的全部或者部分进行任何形式的复制、传输、披露、修订、修改或使用。违反者将对其违反行为所造成的任何以及全部损害承担责任,码灵保留采取任何法律所允许范围内救济措施的权利。

# 术语定义

下面的是本手册中用到的有关术语的缩写、英文全称和中文解释。

PWM Pulse Width Modulation

脉冲宽度调制

MCU Main Control Unit

主控单元

ARM Advanced RSIC Machine

AMBA Advanced Microcontroller Bus Architecture

先进微控制器总线体系结构

AXI Advanced eXtensible Interface

先进可扩展接口

AHB Advanced High performance Bus

先进高性能总线

APB Advanced Peripheral Bus

先进外围总线

SoC System on Chip

片上系统

MAC Multiplier and Accumulator

乘加器

ALU Arithmetic and Logic Unit

算术逻辑单元

JTAG Joint Test Action Group

联合测试行动组

# 目录

| CFW32C7UL     | 应用概要                 | 1    |

|---------------|----------------------|------|

| 郑重声明          |                      | 2    |

| 术语定义          |                      | 3    |

| 目录            |                      | 4    |

| 1 概述          |                      | 6    |

| <b>1.1</b> 芯片 | 功能架构                 | 6    |

| 1.2 功能        | 特点                   | 6    |

| 1.3 芯片        | 工作模式                 | 11   |

|               | Ⅰ 开机阶段               |      |

| 1.3.2         | 2 工作阶段               | 12   |

| 1.3.3         | 3 关机阶段               | 12   |

| 2 管脚分配和       | 信号描述                 | 13   |

| <b>2.1</b> 符号 | 说明                   | 13   |

| 2.2 芯片        | 管脚列表                 |      |

| 2.2.          | <b>!</b> 电源管脚列表      | 14   |

| 2.2.2         | 2 模拟管脚列表             | 16   |

| 2.2.          | 3 LPDDR 接口管脚列表       | 18   |

| 2.2.4         | <b>1</b> 功能管脚列表      | 20   |

| 3 电气特性        |                      | 26   |

| <b>3.1</b> 工作 | 环境极限范围               | 26   |

| 3.2 工作        | 环境推荐值                | 27   |

| 3.3 管脚        | AC/DC 参数             | 28   |

| 3.3.          | I MEMCTL IO AC/DC 参数 | 28   |

| 3.3.2         | 2 其他 IO AC/DC 参数     | 29   |

| 3.4 时钟        | 特性                   | . 29 |

| 3.4.          | I 32KHz 时钟           | 30   |

| 3.4.2         | <b>2</b> 16MHz 时钟    | 30   |

| 3.5 上电时序                     | 30         |

|------------------------------|------------|

| <b>3.6</b> Memory 接口时序       | 31         |

| 3.6.1 MEMCTL                 | 32         |

| <b>3.6.2</b> Nand FLASH 接口时序 | 错误! 未定义书签。 |

| <b>3.7</b> SSI 接口时序          | 33         |

| <b>3.7.1</b> SPI 协议接口时序      | 33         |

| <b>3.7.2</b> SSP 协议接口时序      | 35         |

| 3.8 I2C 接口时序                 | 35         |

| 3.9 I2S 接口时序                 | 36         |

| 4 机械特性                       | 38         |

| 4.1 封装材料                     |            |

| 4.2 机械尺寸图                    | 39         |

| <b>4.3</b> 分类特征              | 40         |

|                              |            |

## 1 概述

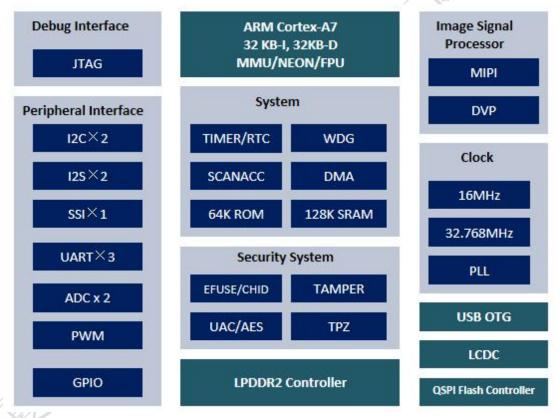

#### 1.1 芯片功能架构

CFW32C7UL 是一款低成本 32 位 SOC 芯片,面向泛工业领域应用的嵌入式高性能应用处理器。CFW32C7UL 芯片采用主流 ARM 内核(Cortex™—A7)和 AMBA 3 总线架构,内置 16 位 DDR 控制器并提供丰富的外设接口。针对二维码识读应用需求,芯片提供 MIPI-DVP 接口,大幅度提高客户选择外部传感器芯片的范围。芯片内置 ISP 图像预处理模块和硬件加速算法,进一步提高二维码识读的处理效率,简化软件处理流程。芯片提供外置 FLASH 高速接口并集成安全加密算法模块,防止反向破解,有效保护客户的软件数据。

CFW32C7UL的结构框图如图 1-1所示。

图 1-1 CFW32C7UL 结构框图

#### 1.2 功能特点

#### 系统特性:

- 采用高性能、低功耗 CMOS 技术

- ▶ 40 纳米 LP (Low-Power) 工艺制造

- ➤ Core 电压 1.1V

- ▶ IO 电压

- ◆ XTAL 32K 电压为 3.3V

- ◆ XTAL 16M 电压为 3.3V

- ◆ PLL 电压为 3.3V

- ◆ EFUSE 电压为 2.5V/3.3V

- ◆ USB OTG PHY 电压为 3.3V

- ◆ MIPI PHY 电压为 2.5V

- ◆ DDR PHY 电压为 1.2V

- ◆ (DDR PHY 参考电压 = 0.5 \* DDR PHY 电压)

- ◆ FLASH 接口电压为 3.3V

- ◆ LCD PANEL 接口电压为 3.3V

- ◆ I2S(0/1), UART(0/1/2), SSI, I2C(0/1), PWM, GPIO, JTAG 电压为 3.3V

- 处理器

- ➤ ARM® Cortex™-A7 Processor

- ➤ 32KB 的指令 CACHE 和 32KB 的数据 CACHE

- ➤ 支持所有的 ARMv7 指令集

- ▶ 支持动态跳转预测及 SECURITY 扩展

- ▶ 集成了标准的 CORESIGHT 组件

- ▶ 支持 NEON 加速,集成 FPU 硬件浮点协处理单元

- ▶ 支持 MMU (Memory Management Unit)

- 采用 AMBA 总线结构

- 低功耗特性:

- ▶ 支持断电功能,仅RTC工作;

- ▶ MEMCTL 支持低功耗模式;支持时钟频率动态调整

- ▶ 支持总线动态频率调整

- ▶ 支持 AXI 低功耗策略

- ▶ 所有模块时钟可以单独关闭

- 调试特性:

- ▶ 可通过 CORESIGHT 子系统调试 Cortex-A7

- 封装特性:

- > LFBGA 13.0x13.0 307P 0.65PITCH

- ► LFBGA 10x10 217P 0.65PITCH

#### 模块简述:

- 复位系统

- ▶ 外部上电/欠压复位(POR/BOR)

- ➤ WDT 复位

- ▶ 软件复位

- ➤ 软件重载 (Bootloader)

- ▶ 单模块独立软复位

- 时钟源

- ▶ 内置 32768Hz 晶振

- ▶ 内置 16MHz 晶振

- ▶ 内置 PLL, 160-1000MHz

- 存储器

- ➤ 64KB ROM: Bootloader:

- ➤ 128KB SRAM:

- ➤ Cortex-A7 内部 RAM

- ◆ 32KB 指令 CACHE

- ◆ 32KB 数据 CACHE

- ➤ 32B eFuse:

- ◆ 12B Chip ID

- ◆ 16B KEY

- ◆ 2B Func Flag

- ◆ 1B Bypass Detect

- ◆ 1 Bit external read lock

- ▶ 内置 DDR CTL

- ◆ 数据宽度 16 位,最高速度 800mbps;

- ◆ 接口频率软件可控;

- ◆ 主控设备: Cortex-A7, DMA;

- ➤ 外置 Flash:

- ◆ SPI 接口, 支持 DUAL 和 QUAD 模式;

- ◆ 支持 DMA 接口;

- ◆ 支持 XIP 模式;

- TPZ 安全控制器

- ▶ 划分 DDR 的安全区域及其属性

- ▶ 实现对 DDR 访问权限的配置

- ▶ 支持安全区域的配置锁定

- ▶ 随机数产生

- ▶ 提供 TPZ 对 DDR 越权访问产生的中断

- ▶ 提供随机数产生中断

- > 支持中断使能和中断屏蔽

- DMA 模块

- ▶ 内含8个通道,通道优先级可编程

- ▶ 通道支持二维传输

- ▶ 通道的源地址和目的地址均可编程

- ▶ 通道数据传输单位为 Byte, 支持地址不对齐传输

- ▶ 通道传输 X 块(X Size) 大小可编程,配置范围为 1 Byte ~ 65535 Bytes

- ▶ 通道传输 X 块个数 Y (Y Size) 大小可编程,配置范围为 1 ~ 65535

- ▶ 支持链表方式传输,内含 4KB的 RAM 用于存储链表

- ▶ 支持强制关闭通道

- > 支持低功耗模式

- ISP

- ▶ AECAGC,自动曝光和增益控制

- ▶ AWB,自动白平衡

- ▶ AFC, 自动对焦

- ▶ DPC, 坏点检测

- ▶ LENC, 镜头阴影校正

- ▶ CCM, 色彩校正矩阵

- ▶ 50/60Hz 灯光闪烁消除

- ▶ 增强色彩插值(去马赛克)

- ▶ 伽马校正

- ▶ 图像降噪

- ▶ 锐化增强

- ▶ 亮度、饱和度、色度和对比度控制

- ▶ 数字变焦(放大 4x,缩小 16x)

- ▶ ARC, 自动动态范围控制(仅支持 HDR)

- ▶ 闪光灯控制

- ▶ 机械快门控制

- ▶ 支持并行 10-bit DVP 输入接口

- MIPI

- ▶ 支持 MIPI CSI-2 接口标准

- ➤ 支持 4-LANE

- SECURITY

- ▶ 支持 CHIP ID

- ▶ 内置 EFUSE

- ▶ 支持低功耗模式

- CIPHER

- ▶ 支持标准 AES 算法和 AES-CM、AES-F8 算法

- > 密钥长度 128bits、192bits、256bits

- ▶ 分组数据支持内嵌 DMA 和 CPU 两种输入方式

- ➤ 标准 AES 算法支持加解密操作

- ➤ AES-CM、AES-F8 算法只支持加密操作

- USB

- ▶ 支持 USB 2.0 高速,全速,低速模式

- ▶ 支持 OTG

- ▶ 支持主机(HOST)和设备(DEVICE) 模式

- 串行接口

- ➤ 2路I2C

- ◆ 支持7位、10位地址方式

- ◆ 支持 master/slave 模式

- ▶ 2路I2S

- ◆ 支持标准 I2S 串口协议

- ◆ 支持 master/slave 模式

- ◆ 支持 TDM 接口

- ◆ 支持 DMA 模式;

- ▶ 1路SSI

- ◆ 收发模式分别具有 16\*16 独立 FIFO;

- ◆ 支持 Motorola SPI 协议和 TI SSP 协议;

- ◆ 支持 master/slave 模式;

- ◆ 支持 DMA 模式;

- ➤ 3路UART

- ◆ 收发模式分别具有 32\*8 独立 FIFO;

- ◆ 支持自动流控 AFC 模式

- ◆ 支持可编程 THRE 中断模式

- ◆ 支持 DMA 模式;

- 定时器模块

- ▶ 7路32位通用定时器 TIMER

- ▶ 32 位看门狗定时器,溢出后可配置复位全芯片或 CPU

- ▶ RTC 模块,使用内部时钟

- PWM

- ▶ 4 通道 8 位 PWM 产生器

- ▶ PWM 工作时钟可调,默认频率是 3.25MHz

- ▶ 输出的 PWM 信号的默认频率范围约为 127Hz~32.5KHz

- ▶ 最大驱动电流: 50mA

- ADC

- ▶ 2 通道 12 位 ADC

- ▶ 参考高电压:内部 VDD

- GPIO

- ▶ 最多可达 128 个 GPIO (包含复用引脚)

- ▶ 可配置 4 种 IO 模式

- ◆ 上拉输入

- ◆ 下拉输入

- ◆ 推挽输出

- ◆ 开漏输出

- ▶ 灵活的中断配置

- ◆ 触发类型设置(边沿检测、电平检测)

- ◆ 触发电平设置(高电平、低电平、双电平)

- UAC

- ▶ 支持的算法类型: SM2、SM3、SM4、HRNG、DIV:

- ▶ 内部包含 4K 字节大小的专用算法 SRAM。

- ▶ 专用算法 SRAM 可以开放给 CPU 访问。

- LCDC

- ▶ 支持多种视频输出接口

- ▶ 画中画:支持8层图层

- ◆ 各图层均支持可调整的横纵向位置

- ◆ 支持 16 级 alpha 混合: 图层级/像素级 (仅支持 24bit RGB888 模式)

- ◆ 支持图层的关键色(color key)功能

- ▶ 各图层可支持尺寸为 2x2~4096x4096

- ▶ 部分显示: 通过 180 接口支持 LCD 的部分显示功能

- ▶ I80 初始化配置方式:通过 Command FIFO 传送内部配置文件,包括一些如延时等的自定义命令。

- ▶ 对 MPU 接口类型的液晶屏,可编程 AC 时序参数

- ▶ 对 RGB 接口类型的液晶屏,可编程 RGB 时序参数

- ▶ 可支持 MPU 接口类型的双 LCD 屏

- ▶ 输出抖色处理(dither)

- ▶ 支持对 LCD 屏的 12/16/18/24b 的多种数据输出格式

#### ARITH ACC

- ▶ 32bit AHB 总线接口用于配置寄存器

- ▶ 64bit AXI 总线接口和 DDR 之间进行数据传输

- ▶ 内置 DMA,支持双向双通道读写

- ▶ DMA 传输速率可控,支持 LLI 传输

- ▶ 支持图像长宽可配,最大(1920x1080)(单位 Byte)

- ▶ 支持多种码制识别

- ▶ 支持污染二维码图像识别,识别率高

- ▶ 支持图像自动搜寻及裁切

- ▶ 支持二值化图像

- ▶ 支持软件配置大津算法阈值及二值化阈值

- ▶ 支持图像重整及旋转

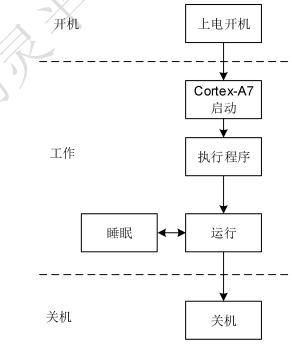

#### 1.3 芯片工作模式

芯片的工作状态可分为开机、工作、关机3个阶段,这3个阶段的特点如下:

- 开机:

- ▶ 芯片上电开机后, AP PWR 首先开始工作, 引导 CPU 进行启动

- 工作:

- ➤ 工作状态: CPU 和模块正常执行功能

- ▶ 睡眠状态: CPU 和模块关闭时钟或关闭电源

- 关机:

- ▶ 一般由软件来完成

图 1-2 给出了芯片工作状态示意图。

图 1-2 工作状态图

#### 1.3.1 开机阶段

芯片一上电就进入开机阶段。在开机阶段中,芯片需要依次经历 32K (clk32k) 时钟起振、16M 时钟起振(OSC16M)、PLL 起振 3 个过程。在开机阶段结束后,芯片内各模块时钟稳定,进入工作阶段。

- 在外部 32K 时钟起振过程中,芯片上电复位信号 prst\_n 需要保持低电平,以确保芯片在 clk32k 稳定之前始终处于全局复位状态。clk32k 稳定后,prst\_n 变为高电平,使芯片退出全局复位状态。

- 在 prst\_n 为高 3 个 32K 时钟周期后,osc\_en\_3v(设置 GPIO[85]复用为 osc\_en\_3v)输出高电平,进入外部 16M 时钟起振过程。16M 时钟起振的时间在开 机阶段固定为 5ms(由 AP\_PWR 内部计数器规定),所以用户必须保证 16M 时 钟在 5ms 内稳定。

- 5ms 后,芯片进入 PLL 起振过程,起振时间在开机阶段固定为 1.125ms。

•

整个开机阶段持续时间大致为(上电后 prst\_n 为低的时间+3 个 32K 时钟周期+6.125ms)。

上电开机完成后,Cortex-A7 自动进入启动过程,即由 AP\_PWR 控制结束 Cortex-A7 的复位并为其提供时钟,随后 Cortex-A7 处于工作状态,开始执行程序。

#### 1.3.2 工作阶段

- 芯片在工作阶段中,分为运行和睡眠两种状态。当 AP 处于运行状态时,AP\_PWR 模块监视 Cortex-A7 及 DMA 的工作状态,如果 Cortex-A7 及 DMA 进入了休眠状态,且睡眠的其它条件满足,则 AP\_PWR 启动睡眠流程,使 AP 进入睡眠状态。

- 在睡眠状态中,由于芯片内部绝大部分模块所需时钟得以关闭,且具有独立电源域模块的电源可处于关断状态,因此芯片处于低功耗状态。

AP\_PWR 在睡眠状态中监视芯片的中断状态(此处中断指的是 Cortex-A7 任意中断源发出的中断),例如,当发生 AP\_PWR 内部 AP\_PWR\_TM 定时中断,外部中断如 AP\_TIMER中断、外接 USB 从挂起到恢复时产生的唤醒中断等时,AP\_PWR 执行唤醒流程,控制 AP从睡眠状态回到运行状态。

#### 1.3.3 关机阶段

芯片在运行状态中,当处理器收到相应的触发条件(如长按关机键)后,控制芯片进入 关机阶段。在关机阶段中,应用程序根据需要执行一些保存操作,执行相关信息的保存(如 保存到 NAND FLASH 中),然后通过控制 PWEN 管脚(或者 PWEN\_CTL 管脚)使 PMU 芯片关闭芯片的供电。

## 2 管脚分配和信号描述

#### **2.1** 符号说明

- 管脚名称:对应芯片封装的 BALL 的名称。

- 信号名称:表示此管脚对应芯片内部功能模块的功能信号。

- 管脚的属性描述

- ▶ I: 数字输入

- ▶ O: 数字输出

- ▶ IO: 数字双向

- ➤ AI: 模拟输入

- ➤ AO: 模拟输出

- > AIO: 模拟双向

- 驱动能力:管脚支持的驱动能力,其中"d"表示上电复位的默认驱动能力。

- 复位方向:芯片复位后,双向 IO 管脚默认方向。

- 复位默认值:芯片复位后,输出类型管脚的默认输出值。

- 上下拉控制:

- ▶ NA:输出管脚以及内部既不接上拉电阻也不接下拉电阻的输入管脚。

- ▶ 详细配置方法请参考管脚复用控制器中管脚上下拉控制寄存器章节。

- 每个管脚名称对应的信号名称/属性/功能描述如下,第一行为默认功能,第二行为第二功能,第三行为第三功能, 第四行为第四功能,默认情况下为第一功能。详细配置方法请参考管脚复用控制器中管脚复用控制寄存器章节。

## 2.2 芯片管脚列表

## **2.2.1** 电源管脚列表

| 名称              | 功能                       | 电压    | 备注        |

|-----------------|--------------------------|-------|-----------|

| Cortex-A7 等所有逻辑 | -<br>計単元                 | Z X   |           |

| VDD_CORE        | 数字 Core 电源 / IO PAD 前驱电源 | 1.1 V |           |

| VDD_IO          | 数字 IO 电源 / IO PAD 后驱电源   | 3.3V  |           |

| Oscillator      |                          |       |           |

| 32K_VDD_AO      | 32K 晶振 Core 电源           | 1.1 V | Always On |

| 32K_VDD_IO_AO   | 32K 晶振 IO 电源             | 3.3V  | Always On |

| 32K_VSS_CORE    | 32K 晶振电源                 | Groud |           |

| 32K_VSS_IO      | 32K 晶振电源                 | Groud |           |

| 16M_VDD_CORE    | 16M 晶振 Core 电源           | 1.1 V |           |

| 16M_VDD_IO      | 16M 晶振 IO 电源             | 3.3V  |           |

| 16M_VSS         | 16M 晶振电源                 | Groud |           |

| PLL_VDD_CORE    | PLL Core 电源              | 1.1 V |           |

| PLL_VDD_IO    | PLL IO 电源         | 3.3V     |                      |

|---------------|-------------------|----------|----------------------|

| PLL_VSS       | PLL 电源            | Groud    |                      |

| RTC           |                   | _        | <b>△</b> , V         |

| RTC_VDD_AO    | RTC 的数字 Core 电源   | 1.1 V    | Always On            |

| RTC_VDD_IO_AO | RTC 的数字 IO 电源     | 3.3V     | Always On            |

| RTC_VSS       | RTC 的数字 Core 电源   | Groud    |                      |

| Efuse         |                   | 4        |                      |

| EFUSE_VDD_IO  | Efuse IO 电源       | 3.3V     |                      |

| EFUSE_AVDD    | Efuse 编程电源        | 2.5V     |                      |

| EFUSE_VSS     | Efuse 电源          | Groud    |                      |

| DDR CTL       | 1/-               |          |                      |

| VDD           | DDR CTL 的 Core 电源 | 1.1 V    |                      |

| VSS           | DDR CTL 的 Core 电源 | Groud    | 全局数字地线               |

| VDDQ          | DDR CTL 的 IO 电源   | 1.2V     | 为了降低噪声,在芯片上进行了<br>隔离 |

| VSSQ          | LPDDR 的 IO 电源     | Groud    | 为了降低噪声,在芯片上进行了<br>隔离 |

| VREF_D        | LPDDR 的参考电源       | 0.5*VDDQ | 在所有时刻都必须保持规定的        |

|               |                 |       | 电压                     |

|---------------|-----------------|-------|------------------------|

| FLASH         |                 |       |                        |

| NFC_VDD_IO_A1 | Flash 接口电源      | 3.3V  | <i>&gt;</i> , <i>∨</i> |

| NFC_VDD_IO_A2 | Flash 接口电源      | 3.3V  | 57                     |

| NFC_VDD_IO_B1 | Flash 接口电源      | 3.3V  |                        |

| NFC_VDD_IO_B2 | Flash 接口电源      | 3.3V  |                        |

| USB           |                 | 4     |                        |

| USB_DVDD      | USB OTG Core 电源 | 1.1 V |                        |

| USB_VDD330    | USB OTG 电源      | 3.3V  |                        |

| USB_VSSA      | USB OTG 电源      | Groud |                        |

| MIPI          |                 |       |                        |

| MIPI_AVDD     | MIPI PHY 模拟电源   | 2.5V  |                        |

| MIPI_AGND     | MIPI PHY 模拟电源   | Groud |                        |

|               |                 |       |                        |

| <b>2.2.2</b> 模拟 <sup>4</sup> | 管脚列表 |    |    |    |

|------------------------------|------|----|----|----|

|                              | 名称   | 功能 | 属性 | 备注 |

|                              |      |    |    |    |

| Oscillator |                                          |     |                 |

|------------|------------------------------------------|-----|-----------------|

| 32K_XIN    | 32K 晶振输入端                                | AIO | 外接 32768 晶体     |

| 32K_XOUT   | 32K 晶振输出端                                | AIO | 外接 32768 晶体     |

| 16M_XIN    | 16M 晶振输入端                                | AIO | 外接 16M 晶体       |

| 16M_XOUT   | 16M 晶振输出端                                | AIO | 外接 16M 晶体       |

| USB        |                                          |     |                 |

| USB_DP0    | USB0 数据总线 D+                             | AIO |                 |

| USB_DM0    | USB0 数据总线 D—                             | AIO |                 |

| USB_ID0    | USB0 Mini 连接器上区分 Mini- A 和 Mini-B 的指示性管脚 | AIO |                 |

| USB_VBUS0  | USB0 的 VBUS 信号                           | AIO |                 |

| USB_VRES0  | USB0 参考信号                                | AIO | 外接对地 200Ω电阻     |

| USB_XI     | USB0 晶振输入端                               | AIO |                 |

| USB_XO     | USB0 晶振输出端                               | AIO |                 |

| MIPI       |                                          |     |                 |

| MCPHY0REXT | MIPI CSI PHY 外接电阻端口                      | AIO | 6.04KΩ到地线,精度 1% |

| MCPHY0CLKP | MIPI CSI PHY 差分时钟信号                      | Al  |                 |

人

| MCPHY0CLKN  | MIPI CSI PHY 差分时钟信号       | Al |      |

|-------------|---------------------------|----|------|

| MIPI_DATAN0 | MIPI CSI PHY LANE0 差分数据信号 | Al |      |

| MIPI_DATAP0 | MIPI CSI PHY LANE0 差分数据信号 | Al |      |

| MIPI_DATAN1 | MIPI CSI PHY LANE1 差分数据信号 | Al | 1917 |

| MIPI_DATAP1 | MIPI CSI PHY LANE1 差分数据信号 | Al |      |

| MIPI_DATAN2 | MIPI CSI PHY LANE2 差分数据信号 | Al |      |

| MIPI_DATAP2 | MIPI CSI PHY LANE2 差分数据信号 | Al |      |

| MIPI_DATAN3 | MIPI CSI PHY LANE3 差分数据信号 | Al |      |

| MIPI_DATAP3 | MIPI CSI PHY LANE3 差分数据信号 | Al |      |

## **2.2.3** LPDDR 接口管脚列表

| 名称           | 功能           | 属性 | 备注     |

|--------------|--------------|----|--------|

| MEM_DQ[15:0] | LPDDR 接口数据总线 | Ю  | 复位默认输入 |

| MEM_A[15:0]  | LPDDR 接口地址总线 | 0  | 复位值 0  |

| MEM_CK       | LPDDR 接口时钟   | 0  | 复位值 0  |

| MEM_CK_N     | LPDDR 接口反向时钟 | 0  | 复位值 1  |

| MEM_CKE        | LPDDR 接口时钟使能信号         | 0 | 复位值 0, 高有效         |

|----------------|------------------------|---|--------------------|

| MEM_CS_N       | LPDDR 接口片选信号           | 0 | 复位值 1, 低有效         |

| MEM_DQS[1:0]   | LPDDR 接口数据 strobe 信号   | Ю | 高有效                |

| MEM_DQS_N[1:0] | LPDDR 接口数据反向 strobe 信号 | Ю | 高有效                |

| MEM_DM[1:0]    | LPDDR 接口数据写保护读使能信号     | 0 | 高有效,分别对应2个字节       |

| MEM_ATO        | LPDDR 接口模拟测试信号         | 0 |                    |

| MEM_DTO[1:0]   | LPDDR 接口数字测试信号         | 0 |                    |

| MEM_ZQ         | LPDDR接口ZQ信号            | Ю | 外接 240Ω电阻到地线,精度 1% |

|                | (输出驱动校准的参考信号)          |   |                    |

| RAM_RST_N      | LPDDR 的复位信号            | 0 |                    |

| MEM_ODT        | LPDDR 的 ODT 信号         | 0 |                    |

| MEM_RAS_N      | LPDDR 的行选择信号           | 0 |                    |

| MEM_CAS_N      | LPDDR 的列选择信号           | 0 |                    |

| MEM_WE_N       | LPDDR 的写使能信号           | 0 |                    |

| MEM_BA[2:0]    | LPDDR 的 BANK 地址线       | 0 |                    |

## 2.2.4 功能管脚列表

| 名称           | 功能            | 属性 | 备注            |

|--------------|---------------|----|---------------|

| TMODE0       | 芯片模式选择位       | 1  | 复位默认悬空        |

| GPIO0~GPIO27 | 通用输入输出 IO     | Ю  | 复位默认输入悬空      |

| GPIO39       | 通用输入输出 IO     | 10 | 复位默认输入悬空      |

| GPIO40       | 通用输入输出 IO     | 10 | 复位默认输入悬空      |

| CLK_OUT0     | 时钟输出信号        | Ю  | 复位默认下拉禁止      |

| CLK_OUT1     | 时钟输出信号        | Ю  | 复位默认下拉禁止      |

| CLK_OUT2     | 时钟输出信号        | Ю  | 复位默认下拉禁止      |

| CLK_OUT3     | 时钟输出信号        | Ю  | 复位默认下拉禁止      |

| OSC_EN_3V    | 16M 时钟的使能信号输出 | Ю  | 复位默认下拉禁止      |

| CLK_PLL_SEL  | PLL 时钟选择端     | I  | 复位默认下拉使能      |

| CLK_PLL_IN   | 外部输入的 PLL 时钟  | I  | 复位默认悬空        |

| RTC_PRST_N   | RTC 模块的外部复位信号 | I  | 固定上拉          |

| PRST_N       | 芯片外部复位信号      | I  | 固定上拉          |

| RST_N        | 复位信号输出        | 0  | 当此管脚设置为复位输出管脚 |

|               |                  |   | 后,<br>若芯片不处于复位状态,管脚输<br>出高阻态;<br>若芯片处于复位状态,管脚输出<br>低电平; |

|---------------|------------------|---|---------------------------------------------------------|

| PWEN_CTL[1:0] | 外部 PMU 使能信号      | 0 | 无上/下拉电阻                                                 |

| PWEN          | 外部 PMU 使能信号      | 0 | 复位默认上拉禁止                                                |

| PMU_DVFS0     | 动态电压调整信号输出       | 0 | 复位默认下拉禁止                                                |

| PMU_DVFS1     | 动态电压调整信号输出       | 0 | 复位默认下拉禁止                                                |

| PWM0          | PWM0 输出信号        | Ю | 复位默认下拉禁止                                                |

| PWM1          | PWM1 输出信号        | Ю | 复位默认下拉禁止                                                |

| PWM2          | PWM2 输出信号        | Ю | 复位默认下拉禁止                                                |

| PWM3          | PWM3 输出信号        | Ю | 复位默认下拉禁止                                                |

| UART0_TX      | UARTO 串行输出信号     | Ю | 复位默认上拉禁止                                                |

| UART0_RX      | UARTO 串行输入信号     | Ю | 复位默认上拉使能                                                |

| UARTO_CTS     | UART0 发送清除信号,低有效 | Ю | 复位默认上拉使能                                                |

| UARTO_RTS     | UART0 发送请求信号,低有效 | Ю | 复位默认下拉禁止                                                |

| UART1_TX      | UART1 串行输出信号     | Ю | 复位默认上拉禁止                                                |

| UART1_RX   | UART1 串行输入信号     | Ю  | 复位默认上拉使能 |

|------------|------------------|----|----------|

| UART1_CTS  | UART1 发送清除信号,低有效 | Ю  | 复位默认上拉使能 |

| UART1_RTS  | UART1 发送请求信号,低有效 | Ю  | 复位默认下拉禁止 |

| UART2_TX   | UART2 串行输出信号     | Ю  | 复位默认上拉禁止 |

| UART2_RX   | UART2 串行输入信号     | Ю  | 复位默认上拉使能 |

| UART2_CTS  | UART2 发送清除信号,低有效 | 10 | 复位默认上拉使能 |

| UART2_RTS  | UART2 发送请求信号,低有效 | 10 | 复位默认下拉禁止 |

| I2C0_SCL   | I2C0 时钟信号        | Ю  | 复位默认上拉使能 |

| I2C0_SDA   | I2C0 数据信号        | Ю  | 复位默认上拉使能 |

| I2C1_SCL   | I2C1 时钟信号        | Ю  | 复位默认上拉使能 |

| I2C1_SDA   | I2C1 数据信号        | Ю  | 复位默认上拉使能 |

| I2S0_SDIN  | I2S0 数据输入信号      | Ю  | 复位默认下拉使能 |

| I2S0_SDOUT | I2S0 数据输入信号      | Ю  | 复位默认下拉禁止 |

| I2S0_SCLK  | I2S0 时钟信号        | Ю  | 复位默认下拉使能 |

| 12S0_WS    | I2S0 左右声道选择信号    | Ю  | 复位默认上拉使能 |

| I2S1_DI    | I2S1 数据输入信号      | Ю  | 复位默认下拉禁止 |

| 12S1_DO    | I2S1 数据输入信号      | Ю  | 复位默认下拉禁止 |

| 12S1_CK     | I2S1 时钟信号          | Ю  | 复位默认下拉禁止 |

|-------------|--------------------|----|----------|

| 12S1_WS     | I2S1 左右声道选择信号      | Ю  | 复位默认下拉禁止 |

| SSI0_TX     | SSI0 数据输出信号        | IO | 复位默认下拉禁止 |

| SSI0_RX     | SSI0 数据输入信号        | IO | 复位默认下拉使能 |

| SSI0_CLK    | SSI0 时钟信号          | Ю  | 复位默认下拉禁止 |

| SSI0_SN0    | SSIO 从设备使能信号       | 10 | 复位默认上拉禁止 |

| SSI0_SN1    | SSI0 从设备使能信号       | IO | 复位默认上拉禁止 |

| ISP_FSIN0   | 帧同步信号              | IO | 复位默认下拉禁止 |

| ISP_PWM     | PWM 信号             | IO | 复位默认下拉禁止 |

| ISP_SCLK0   | Sensor 时钟          | IO | 复位默认下拉禁止 |

| ISP_STROBE  | Sensor 的 strobe 信号 | Ю  | 复位默认下拉使能 |

| ISP_S_DATA0 | Sensor 并行接口数据总线    | Ю  | 复位默认下拉禁止 |

| ISP_S_DATA1 | Sensor 并行接口数据总线    | Ю  | 复位默认下拉禁止 |

| ISP_S_DATA2 | Sensor 并行接口数据总线    | Ю  | 复位默认上拉使能 |

| ISP_S_DATA3 | Sensor 并行接口数据总线    | Ю  | 复位默认上拉使能 |

| SP_S_DATA4  | Sensor 并行接口数据总线    | Ю  | 复位默认上拉使能 |

| ISP_S_DATA5 | Sensor 并行接口数据总线    | Ю  | 复位默认下拉使能 |

| ICD C DATAG  | Sensor 并行接口数据总线     | Ю  | 复位默认下拉使能          |

|--------------|---------------------|----|-------------------|

| ISP_S_DATA6  | OEIISUI 开11 按口数据总线  | 10 | 友型私 <b>从下</b> 型使舵 |

| ISP_S_DATA7  | Sensor 并行接口数据总线     | Ю  | 复位默认下拉使能          |

| ISP_S_DATA8  | Sensor 并行接口数据总线     | Ю  | 复位默认下拉使能          |

| ISP_S_DATA9  | Sensor 并行接口数据总线     | Ю  | 复位默认下拉使能          |

| ISP_S_DATA10 | Sensor 并行接口数据总线     | 10 | 复位默认下拉使能          |

| ISP_S_DATA11 | Sensor 并行接口数据总线     | 10 | 复位默认下拉使能          |

| ISP_SCLK     | Sensor 并行接口时钟       | 10 | 复位默认下拉使能          |

| ISP_S_HSYNC  | Sensor 水平同步信号       | IO | 复位默认下拉使能          |

| ISP_S_VSYNC  | Sensor 垂直同步信号       | Ю  | 复位默认下拉使能          |

| ISP_RST_N0   | Sensor 复位信号         | Ю  | 复位默认下拉使能          |

| ISP_PDWN_N0  | Sensor 断电信号         | Ю  | 复位默认上拉禁止          |

| JTAG_TCK     | JTAG 时钟信号           | Ю  | 复位默认下拉禁止          |

| JTAG_TDI     | JTAG 输入信号           | Ю  | 复位默认下拉禁止          |

| JTAG_TDO     | JTAG 输出信号           | Ю  | 复位默认上拉禁止          |

| JTAG_TMS     | JTAG 模式选择信号         | Ю  | 复位默认下拉禁止          |

| JTAG_nTRST   | JTAG 复位信号           | Ю  | 复位默认上拉禁止          |

| QSPI_CLK     | QSPI Flash 的 CLK 信号 | 0  |                   |

| QSPI_CS        | QSPI Flash 的 CS 信号                    | 0  |                        |

|----------------|---------------------------------------|----|------------------------|

| QSPI_HOLD      | QSPI Flash 的 HOLD 信号                  | 0  |                        |

| QSPI_WP        | QSPI Flash 的 WP 信号                    | 0  | <i>&gt;</i> , <i>∨</i> |

| QSPI_DI        | QSPI Flash 的 DI 信号                    | Ю  | 3                      |

| QSPI_DO        | QSPI Flash 的 DO 信号                    | Ю  |                        |

| LCDC_CSM_N     |                                       | 10 | 复位默认下拉使能               |

| LCDC_CSS_N     | LCDC_CSS_N / LCDC_ENABLE              | 10 | 复位默认下拉使能               |

| LCDC_A0        | LCDC_A0 / HSYNC                       | Ю  | 复位默认下拉使能               |

| LCDC_WR_N      | LCDC_WR_N / DOTCLK                    | Ю  | 复位默认下拉使能               |

| LCDC_RD_N      | LCDC_RD_N / VSYNC                     | Ю  | 复位默认下拉使能               |

| LCDC_DATOUT_EN |                                       | Ю  | 复位默认下拉使能               |

| LCDC_DATOUT_0  |                                       | Ю  | 复位默认下拉使能               |

| LCDC_DATOUT_22 |                                       |    |                        |

| LCDC_DATOUT_23 |                                       | 0  |                        |

| USB_DRVVBUS    | USB 的 VBUS 输出镜像管脚                     | Ю  | 复位默认下拉禁止               |

|                | · · · · · · · · · · · · · · · · · · · |    |                        |

# 3 电气特性

本章包括 CFW32C7UL 芯片的电气特性极限值以及推荐值。 在本文其他位置提到的相关 AC/DC 参数除特别说明外都是推荐值。

#### 3.1 工作环境极限范围

本节所列出的所谓"极限范围"是芯片所能承受的极限环境,如果超出此范围或者长时间工作在极限条件下,都有可能对芯片造成不可逆转的损坏。

注意: 在本节所列出的极限环境下并不代表芯片可以稳定工作。

表 3-1 工作环境极限范围表

| Parameter         | Min   | Max  | UNIT         |

|-------------------|-------|------|--------------|

| VDD_CORE          | -0. 5 | 1. 5 | V            |

| VDD_IO            | -0. 5 | 4. 0 | V            |

| 32K_VDD_AO        | -0. 5 | 1. 4 | V            |

| 32K_VDD_IO_AO     | -0. 5 | 4. 0 | V            |

| 16M_VDD_CORE      | -0. 5 | 1. 4 | V            |

| 16M_VDD_IO        | -0. 5 | 4. 0 | V            |

| PLL_VDD_CORE      | -0. 5 | 1.4  | V            |

| PLL_VDD_IO        | -0. 5 | 4. 0 | V            |

| RTC_VDD_AO        | -0. 5 | 1. 4 | V            |

| RTC_VDD_IO_AO     | -0. 5 | 4. 0 | V            |

| EFUSE_VDD_IO      | -0. 5 | 4. 0 | V            |

| EFUSE_AVDD        | -0.5  | 2.75 | V            |

| VDD(LPDDR 内核电压)   | -0. 5 | 1. 4 | V            |

| VDDQ              | -0. 5 | 2.1  | V            |

| VREF_D            | -0. 4 | 1. 5 | V            |

| NFC_VDD_IO_*      | -0.5  | 4. 0 | V            |

| USB_DVDD          | -0. 5 | 1. 5 | V            |

| USB_VDD330        | -0.5  | 4    | V            |

| MIPI_AVDD         | -0.5  | 2.75 | V            |

| 工作温度( <b>Tj</b> ) | -40   | 125  | $^{\circ}$ C |

## 3.2 工作环境推荐值

表 3-2 工作环境推荐值

|                                                | 表 3-2 工作环境技 | E存阻<br>Min   | Nom          | Max          | UNIT |

|------------------------------------------------|-------------|--------------|--------------|--------------|------|

| \(\(\mathbb{P}\) \(\mathbb{P}\) \(\mathbb{P}\) |             |              |              |              |      |

| VDD_CORE                                       |             | 0.99         | 1.1          | 1.21         | V    |

| VDD_IO                                         |             | 3            | 3.3          | 3.6          | V    |

| 32K_VDD_AO                                     |             | 0.99         | 1.1          | 1.21         | V    |

| 32K_VDD_IO_AO                                  |             | 3            | 3.3          | 3.6          | ٧    |

| 16M_VDD_CORE                                   |             | 0.99         | 1.1          | 1.21         | V    |

| 16M_VDD_IO                                     |             | 3            | 3.3          | 3.6          | V    |

| PLL_VDD_CORE                                   |             | 0.99         | 1.1          | 1.21         | V    |

| PLL_VDD_IO                                     | PLL_VDD_IO  |              | 3.3          | 3.6          | V    |

| RTC_VDD_AO                                     | KX          | 0.99         | 1.1          | 1.21         | V    |

| RTC_VDD_IO_AO                                  |             | 3            | 3.3          | 3.6          | V    |

| EFUSE_VDD_IO                                   |             | 3            | 3.3          | 3.6          | V    |

| EFUSE_AVDD                                     |             | 2.25         | 2.5          | 2.75         | V    |

| VDD(LPDDR 内核电压)                                |             | 0.99         | 1.1          | 1.21         | V    |

| VDDQ                                           | LPDDR2      | 1.15         | 1.2          | 1.25         | V    |

| 3                                              | DDR3        | 1.425        | 1.5          | 1.575        | V    |

| VREF_D                                         |             | 0.5*<br>VDDQ | 0.5*<br>VDDQ | 0.5*<br>VDDQ | V    |

| NFC_VDD_IO_A1                                  |             | 2.7          | 3.3          | 3.6          | V    |

| USB_DVDD                                       |             | 0.99         | 1.1          | 1.21         | V    |

| USB_VDD330                                     |             | 3            | 3.3          | 3.6          | V    |

| MIPI_AVDD                                      |             | 2.25         | 2.5          | 2.75         | V    |

| 备注:                                            |             | ı            |              | 1            |      |

## **3.3** 管脚 AC/DC 参数

本节分别列出了 MEMCTL 以及其他 IO 的 AC/DC 参数。

## 3.3.1 MEMCTL IO AC/DC 参数

表 3-3 MEMCTL IO AC/DC 参数

| Symbol    | Parameters                    | Min            | Nom       | Max            | UNIT     |

|-----------|-------------------------------|----------------|-----------|----------------|----------|

| MEMCTL IO | O AC/DC 参数(LPDDR2)            | VDDcore = 1.1V | VDDIO = 1 | .2V Tempe      | rature = |

| 25℃)      |                               |                |           |                |          |

| VDD       | Core supply voltage           | 0.99           | 1.1       | 1.21           | V        |

| VDDQ      | HSUL output supply voltage    | 1.14           | 1.2       | 1.3            | V        |

| VREF      | HSUL reference supply voltage | 0.49*VDDQ      | 0.5*VDDQ  | 0.51*VDD<br>Q  | V        |

| VIH(DC)   | DC input voltage High         | VREF+0.13      |           | VDDQ           | V        |

| VIL(DC)   | DC input voltage Low          | VSSQ-0.3       |           | VREF-0.1<br>3  | V        |

| VIH(AC)   | Input logic threshold High    | VREF+220m<br>V |           |                | mV       |

| VIL(AC)   | Input logic threshold Low     | XX             |           | VREF-22<br>0mV | mV       |

| VOH       | DC output logic High          | 0.9*VDDQ       |           |                | V        |

| VOL       | DC output logic Low           |                |           | 0.1*VDD<br>Q   | V        |

| IDDQ      | VDDQ standby current          |                | 0.02      | 12.31          | uA       |

| IDD       | VDD quiescent current         |                | 0.02      | 4.21           | uA       |

| IDDQ      | Output Low IDDQ DC current    |                | 0.3       | 0.79           | mA       |

| IDDQ      | Output High IDDQ DC current   |                | 0.28      | 0.76           | mA       |

| IDDQ      | Input Low IDDQ DC current     |                | 0.30      | 0.79           | mA       |

| IDDQ      | Input High IDDQ DC current    |                | 0.28      | 0.76           | mA       |

| ILL       | Input leakage current         |                | 0.01      | 4.51           | uA       |

## **3.3.2** 其他 IO AC/DC 参数

本节介绍除 MEMCTL 模块之外的其他 IO 的 AC/DC 参数。

表 3-4 其他 IO AC/DC 参数

| 其他 IO A            | C/DC 参数(VDDcore = 1.1V VDD <sub>IO</sub> = 3.3                              |      | erature = | : 25℃) |    |

|--------------------|-----------------------------------------------------------------------------|------|-----------|--------|----|

| V <sub>IL</sub>    | Input Low Voltage                                                           | -0.3 |           | 0.8    | ٧  |

| V <sub>IH</sub>    | Input High Voltage                                                          | 2    |           | 3.6    | V  |

| V <sub>T</sub>     | Threshold Point                                                             | 1.34 | 1.46      | 1.6    | V  |

| V <sub>T+</sub>    | Schmitt Trigger Low to High Threshold Point                                 | 1.69 | 1.83      | 1.96   | V  |

| V <sub>T</sub> -   | Schmitt Trigger Low to Low Threshold Point                                  | 1.21 | 1.32      | 1.46   | V  |

| V <sub>TPU</sub>   | Threshold Point with Pull-up Resistor Enabled                               | 1.33 | 1.44      | 1.59   | V  |

| $V_{TPD}$          | Threshold Point with Pull-down Resistor Enabled                             | 1.36 | 1.47      | 1.6    | ٧  |

| $V_T^+_{PU}$       | Schmitt Trigger Low to High Threshold Point with Pull-up Resistor Enabled   |      | 1.82      | 1.94   | ٧  |

| V <sub>T</sub> -PU | Schmitt Trigger High to Low Threshold Point with Pull-up Resistor Enabled   | 1.2  | 1.31      | 1.45   | V  |

| $V_{T}^{+}_{PD}$   | Schmitt Trigger Low to High Threshold Point with Pull-down Resistor Enabled | 1.71 | 1.84      | 1.97   | ٧  |

| V <sub>T</sub> -PD | Schmitt Trigger High to Low Threshold Point with Pull-down Resistor Enabled | 1.23 | 1.33      | 1.46   | ٧  |

| l <sub>l</sub>     | Input Leakage Current @ VI=3.3V or 0V                                       |      |           | ±10µ   | Α  |

| l <sub>oz</sub>    | Tri-state Output Leakage Current @ VO=3.3V or 0V                            |      |           | ±10µ   | А  |

| R <sub>PU</sub>    | Pull-up Resistor                                                            | 41K  | 60K       | 91K    | Ω  |

| R <sub>PD</sub>    | Pull-down Resistor                                                          | 43K  | 63K       | 103K   | Ω  |

| VoL                | Output Low Voltage                                                          |      |           | 0.4    | V  |

| Vон                | Output High Voltage                                                         | 2.4  |           |        | V  |

| loL                | Low Level Output Current @VOL(max)                                          |      |           |        | mA |

|                    | 12mA:                                                                       | 17.5 | 27        | 36.5   |    |

| \17                | 16mA:                                                                       | 21.9 | 33.8      | 45.7   |    |

| Іон                | High Level Output Current @VOH(min)                                         |      |           |        | mA |

|                    | 12mA:                                                                       | 24.8 | 49.1      | 82.9   |    |

|                    | 16mA:                                                                       | 33.1 | 65.4      | 110.5  |    |

## **3.4** 时钟特性

本节介绍了 CFW32C7UL 芯片时钟输入信号的特性。CFW32C7UL 有 1 个 32K 时钟输入和 1 个 16MHz 时钟输入。

#### 3.4.1 32KHz 时钟

CFW32C7UL 芯片 32768Hz 时钟信号由芯片内部产生(需要外接晶体)。

#### 3.4.2 16MHz 时钟

CFW32C7UL 芯片 16MHz 时钟信号由芯片内部产生(需要外接晶体)。

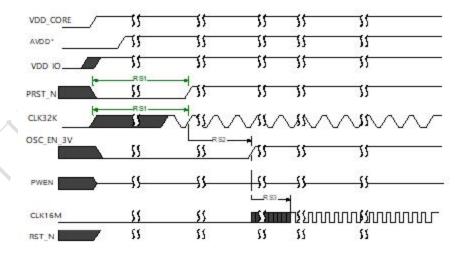

#### 3.5 上电时序

本节提供了 CFW32C7UL 在开机阶段的上电、硬件复位及关键信号时序图。图 3-1 给出了开机复位的时序示意图,表 3-5 列出了相关参数。

|     | 71 0 0 0 110 0 0 110 0 0 0 0 0 0 0 0 0 0 |                            |     |     |    |

|-----|------------------------------------------|----------------------------|-----|-----|----|

| 序号  | 名称                                       | 描述                         | 最小值 | 最大值 | 单位 |

| RS1 | t <sub>w</sub> (prst_n)                  | Pulse duration. prst_n low | N   |     | ns |

| RS2 | t <sub>d</sub> (prst_nH-osc_enH)         | Delay time. prst_n high to |     | 6P  | ns |

|     |                                          | osc_en high                |     |     |    |

| RS3 | t <sub>W</sub> (26MHz oscillator         | Pulse duration, 26MHz      |     | 5   | ms |

|     | start-up time)                           | oscillator start-up time   |     |     |    |

表 3-5 CFW32C7UL 开机复位时序参数表

注 1: P=period of 32KHz clock

注 2: N=32KHz oscillator start-up after stable power

图 3-1 CFW32C7UL Power-on Reset Timing Diagram

VDD\_CORE:包括 VDD\_CORE、32K\_VDD\_AO、16M\_VDD\_CORE、VDD、PLL\_VDD\_CORE、RTC\_VDD\_AO、USB\_DVDD

AVDD: 包括 PLL\_VDD\_IO、USB\_VDD330、MIPI\_AVDD

VDD-IO:包括 VDD\_IO、32K\_VDD\_IO\_AO、16M\_VDD\_IO、EFUSE\_VDD\_IO、

RTC\_VDD\_IO\_AO、VDDQ、VREF\_D 、NFC\_VDD\_IO\_\*

PRST N:来自片外的输入信号,用作全芯片的上电复位信号

RST\_N: 芯片的输出信号,AP\_PWR内部产生的异步复位信号RST\_N(低电平复位)控制整个芯片一直处于异步复位中,并且送出到片外供其他需要和芯片同时复位的器件使用

OSC EN 3V: 芯片的输出信号, 16M 时钟所需的使能信号

PWEN: 送给电源管理芯片的电源使能控制信号

◆32K\_VDD\_AO、32K\_VDD\_IO\_AO、RTC\_VDD\_AO、RTC\_VDD\_IO\_AO 为 RTC 模块(always on 模块,包含 32K 振荡器)的供电管脚。在芯片上电后,不能被关 断,但可以通过 PWEN\_CTL[1:0]信号控制外部 PMU,以便关断 RTC 模块以外的 Core 电源及 IO 电源。

CFW32C7UL 芯片对内核电源与 IO 电源的上电次序没有要求,建议先给内核电源供电再给 PHY 和 PLL 电源供电。

CFW32C7UL 芯片的上电异步复位信号 PRST\_N 的有效时间由 32K 时钟稳定时间决定。PRST\_N 必须至少保持低电平到 32K 时钟稳定,才能保证芯片处在正确的初始状态。32K 时钟的稳定时间与 32K 晶体的性能及负载电容 CL 相关。

CFW32C7UL 芯片输出的 OSC\_EN\_3V 信号为内置 16MHz 时钟的使能信号的输出。用来判断内置 16MHz 晶体振荡器是否使能;另外,当内置的 16MHz 晶体振荡器不能正常起振时,可以用此信号控制外置晶体振荡器。该信号在复位状态为低电平,在深睡状态时可由寄存器配置为低电平或高电平,当 AP 处于工作状态下为高电平。

CFW32C7UL 输出异步复位信号 RST\_N(低电平复位),该信号供片外其他需要和芯片同时复位的器件使用。该信号的复位状态为低电平,在发生内部软复位或者 AP\_WDT 复位的时候为低,并且为低的时间可以通过 AP\_PWR 的寄存器 AP\_PWR\_CHIPRSTN\_CTL 控制。

只要芯片电源、异步复位信号、时钟信号符合以上条件,芯片即进入开机工作状态;如果需要关机必须在工作状态下由软件控制芯片的所有电源关闭来实现。一般推荐由 PMU(电源管理模块)来控制 CFW32C7UL 的开关机。

CFW32C7UL 芯片输出的 PWEN 信号为电源控制信号,与 GPIO 管脚复用。该信号一般用来与 PMU 的电源保持管脚连接。该信号不会被复位,上电后状态不确定,通过写 APWR\_PWEN\_CTL.PWEN\_CTL 为 1,PWEN 送出高电平,写 APWR\_PWEN\_CTL. PWEN\_CTL 为 0,PWEN 送出低电平。在本芯片中,由 BOOTROM 程序负责将 PWEN\_CTL 写为了高电平。

#### 3.6 Memory 接口时序

#### **3.6.1** MEMCTL

#### 3.6.1.1 LPDDR2 接口时序

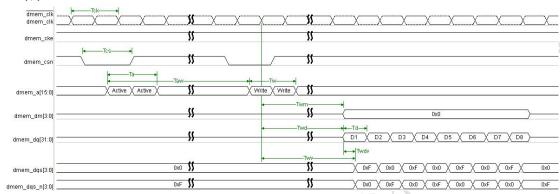

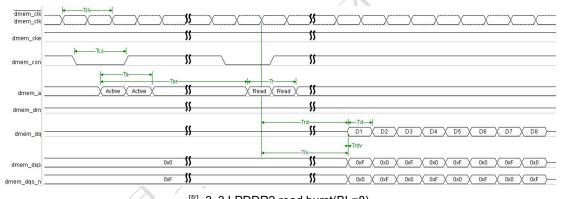

本节通过图 3-2 和图 3-3 介绍了 CFW32C7UL 芯片 MEMCTL1 外接 LPDDR2 的接口时序。

图 3-2 LPDDR2 write burst(BL=8)

图 3-3 LPDDR2 read burst(BL=8)

表 3-6 中列出了 LPDDR2 接口时序参数。

表 3-6 LPDDR2 接口时序参数表

| 编号  | 描述                       | 数值              |

|-----|--------------------------|-----------------|

| Tck | LPDDR2 工作时钟周期            | 寄存器可配           |

| Tcs | cs_n 信号的有效时间             | Tck             |

| Та  | active 命令的时间             | Tck             |

| Tw  | write 命令的时间              | Tck             |

| Tr  | read 命令的时间               | Tck             |

| Taw | active 命令到 write 命令的时间延迟 | TRCD*Tck        |

| Tar | active 命令到 read 命令的时间延迟  | TRCD*Tck        |

| Twm | write 命令到 dm 有效之间的时间延迟   | (TCWL+0.75)*Tck |

| Twd | write 命令到数据总线上数据有效之间的时   | (TCWL+0.75)*Tck |

|     | 间延迟                      |                 |

| Trd | read 命令到数据总线上数据有效之间的时间   | (TCL+0.75)*Tck  |

|     | 延迟                       |                 |

| 编号   | 描述                         | 数值             |

|------|----------------------------|----------------|

| Twv  | write命令到dqs信号首个上升沿之间的时间    | (TCWL+1)*Tck   |

|      | 延迟                         |                |

| Trv  | read 命令到 dqs 信号首个上升沿之间的时间  | (TCL+0.75)*Tck |

|      | 延迟                         |                |

| Td   | 数据线上单个数据有效的时间周期            | 0.5Tck         |

| Twdv | write 操作时,数据总线上数据有效到 dqs 信 | 0.25Tck        |

|      | 号首个上升沿之间的时间延迟              |                |

| Trdv | read 操作时,数据总线上数据有效到 dqs 信  | 0              |

|      | 号首个上升沿之间的时间延迟              |                |

#### 3.7 SSI 接口时序

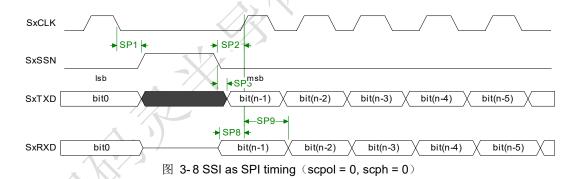

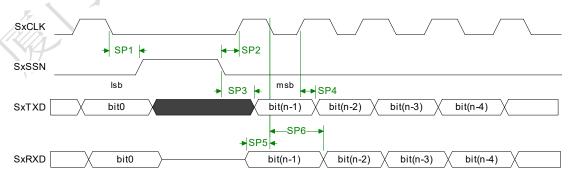

CFW32C7UL 芯片包含四个同步串行接口,可以支持 SPI 和 SSP 接口协议。以下部分介绍了各种协议下的接口时序。以下 AC 参数的测试条件为: T=25℃/RL=50Ω/CL=50pF/CI=10pF/IO driver-strength=default value。

#### 3.7.1 SPI 协议接口时序

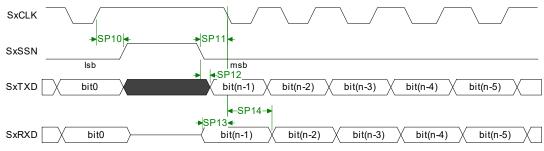

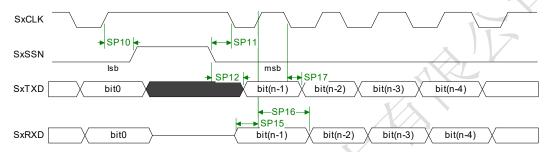

本节通过图 3-8 至图 3-11 介绍了 CFW32C7UL 芯片 SSI 接口配置为 SPI 协议方式下的时序。

图 3-9 SSI as SPI timing (scpol = 0, scph =1)

图 3-10 SSI as SPI timing (scpol = 1, scph =0)

图 3-11 SSI as SPI timing (scpol = 1, scph =1)

表 3-8 SPI Interface 时序参数表

| NO   | Cumphal         | Symbol Description                        |      | PVDD5 = 3 V Nominal |      |

|------|-----------------|-------------------------------------------|------|---------------------|------|

| NO.  | Symbol          | Description                               | MIN  | MAX                 | UNIT |

| SP1  | Th (clkl-ssnh)  | hold time,ssn high after clk low          |      | 0.5T(1)             | ns   |

| SP2  | Td (ssnl-clkh)  | delay time,ssn low to clk<br>high         |      | 0.5T                | ns   |

| SP3  | Td(ssnl-txdv)   | delay time,ssn low to<br>data valid       |      | 0                   | ns   |

| SP4  | Td (clkh-txdv)  | delay time,clk high to<br>data valid      |      | 0                   | ns   |

| SP5  | Tsu (rxdv-clkl) | setup time, data valid<br>before clk low  | 0.5T |                     | ns   |

| SP6  | Th (clkl-rxdv)  | hold time, data valid<br>after clk low    | 0.5T |                     | ns   |

| SP8  | Tsu (rxdv-clkh) | setup time, data valid<br>before clk high | 0.5T |                     | ns   |

| SP9  | Th (clkh-rxdv)  | hold time, data valid<br>after clk high   | 0.5T |                     | ns   |

| SP10 | Th (clkh-ssnl)  | hold time,ssn low after clk high          |      | 0.5T                | ns   |

| SP11 | Td (ssnl-clkl)  | delay time,ssn low to clk<br>low          |      | 0.5T                | ns   |

| NO.   | Symbol          | Description                               | PVDD5 = 3 | LINUT |      |

|-------|-----------------|-------------------------------------------|-----------|-------|------|

| NO.   | Symbol          | Description                               | MIN       | MAX   | UNIT |

| SP12  | Td(ssnl-txdv)   | delay time,ssn low to<br>data valid       |           | 0     | ns   |

| SP13  | Tsu (rxdv-clkl) | setup time, data valid<br>before clk low  | 0.5T      |       | ns   |

| SP14  | Th (clkl-rxdv)  | hold time, data valid<br>after clk low    | 0.5T      |       | ns   |

| SP15  | Tsu (rxdv-clkh) | setup time, data valid<br>before clk high | 0.5T      |       | ns   |

| SP16  | Th (clkh-rxdv)  | hold time, data valid<br>after clk high   | 0.5T      |       | ns   |

| SP17  | Td (clkl-rxdv)  | delay time,clk low to<br>data valid       |           | 0     | ns   |

| Note: | (1)T = cycle of | SxCLK                                     |           |       |      |

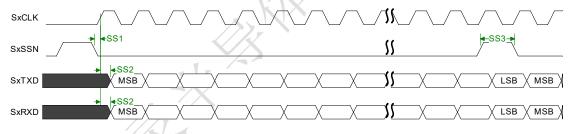

## **3.7.2** SSP 协议接口时序

本节通过图 3-12 介绍了 CFW32C7UL 芯片 SSI 接口配置为 SSP 协议方式下的时序。

图 3-12 SSI as SSP timing

表 3-9 SSP 接口时序参数表

#### (1)T= Cycle of SxCLK

|                                                 |                            |                                      | PVDD5 |       |      |

|-------------------------------------------------|----------------------------|--------------------------------------|-------|-------|------|

| NO.                                             | Symbol                     | Description                          | Non   | ninal | UNIT |

|                                                 |                            |                                      | MIN   | MAX   |      |

| SS1                                             | tclk                       | slave select signal low to clk vaild | 0     | 0     | ns   |

| SS2                                             | tdd                        | clk high to ssi transmit data vaild  | 0     | 0     | ns   |

| SS3 tssnw slave select signal width 1T(1) 1T ns |                            |                                      |       | ns    |      |

| Note                                            | Note: (1)T= Cycle of SxCLK |                                      |       |       |      |

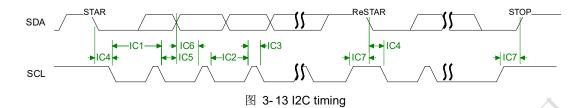

## 3.8 I2C 接口时序

本节通过图 3-13 介绍了 CFW32C7UL 芯片 I2C 接口的时序。I2Cx(x=0~3),COM\_I2C 五个 I2C 接口的时序相同。以下 AC 参数的测试条件为: T=25℃ /RL=50Ω/CL=50pF/Ci=10pF/IO driver-strength=default value。

表 3-10 I2C 接口时序参数表

|     |                |                                                                         | STANE         | DTARD | FA  | ST  |      |

|-----|----------------|-------------------------------------------------------------------------|---------------|-------|-----|-----|------|

| NO. | Symbol         | Description                                                             | МО            | DE    | МС  | DDE | UNIT |

|     |                |                                                                         | MIN           | MAX   | MIN | MAX |      |

| IC1 | tc (SCL)       | cycle time , I2C.SCL                                                    | 10            |       | 2.5 | ľ   | us   |

| IC2 | tw (SCLL)      | pulse duration,I2C.SCL low                                              | 4.7           |       | 1.3 |     | us   |

| IC3 | tw (SCLH)      | pulse duration,I2C.SCL high                                             | 4             |       | 0.6 |     | us   |

| IC4 | th (SCLL-SDAL) | I2C.SCL low after I2C.SDA low (for a START & ReSTART)                   | 4             |       | 0.6 |     | us   |

| IC5 | th (SDA-SCLL)  | Hold time, I2C.SDA valid after I2C.SCL low                              | <b>1T</b> (1) |       | 1T  |     | ns   |

| IC6 | tsu (SDA-SDLH) | Setup time, I2C.SDA valid before I2C.SCL high                           | 250           |       | 100 |     | ns   |

| IC7 | tsu(SDA-SDLH)  | Setup time, I2C.SCL high<br>before I2C.SDA high (for<br>STOP condition) | 4             |       | 0.6 |     | us   |

Note: (1)T=Cycle of i2c\_mclk

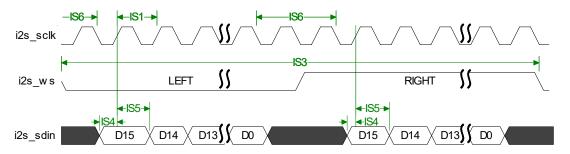

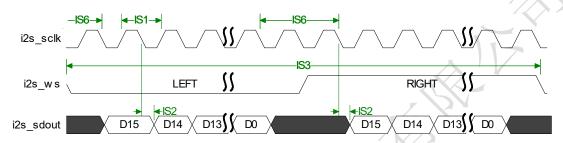

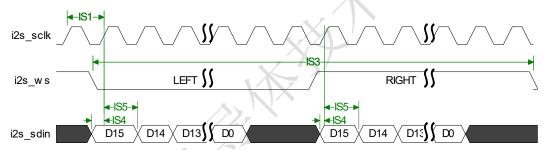

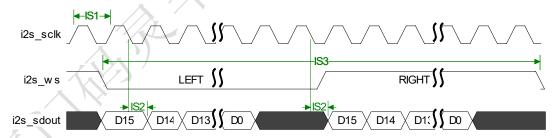

#### 3.9 I2S 接口时序

本节介绍了 CFW32C7UL 芯片 I2S 接口时序。以下 AC 参数的测试条件为: T=25℃/RL=50Ω/CL=50pF/CI=10pF/IO driver-strength=default value。

以下列出了 I2S 接口时序图。

#### 1. I2S 标准接口协议

I2S 工作在 master 模式时 DLY\_MODE 只能为 0, slave 模式下 DLY\_MODE 可以为 0 也可以为 1。

I2S 工作在 slave 模式时,在一个 i2s\_ws 周期中,对于 LEFT 和 RIGHT 声道,必须保证外部输入的 i2s\_sclk 时钟有且只有 16 个上升沿。即图 3-14 和图 3-15 中 IS6 参数标明的时间段内 i2s sclk 可以为高电平也可以为低电平,但不允许出现 i2s sclk 的上升沿。

图 3-14 I2S master/slave rx timing (DLY\_MODE=0)

图 3-15 I2S master/slave tx timing (DLY\_MODE=0)

图 3-16 I2S slave rx timing (DLY\_MODE=1)

图 3-17 I2S slave tx timing(DLY\_MODE=1)

表 3-11 I2S 接口参数表

| NO. | Symbol      | Description                          | PVDD:<br>Non    | UNIT |    |

|-----|-------------|--------------------------------------|-----------------|------|----|

|     |             |                                      | MIN             | MAX  |    |

| IS1 | tc(clk)     | Cycle time, i2s_sclk                 | <b>6T</b> (1)   |      | ns |

| IS2 | td(clkl-dv) | i2s_sclk low to i2s_sdout data valid |                 | 2T   | ns |

| IS3 | tc(clk)     | Cycle time,i2s_ws                    | <b>32T1</b> (2) |      | ns |

| NO. | Symbol       | Description                                                                                                          | PVDD5 = 3 V<br>Nominal |     | UNIT |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------|------------------------|-----|------|

|     |              |                                                                                                                      | MIN                    | MAX |      |

| IS4 | tsuidy cikh) | Setup time, read data(i2s_sdin) valid before i2s_sclk high                                                           | 0                      |     | ns   |

| IS5 | iin(cikn-av) | Hold time, read data(i2s_sdin) valid after i2s_sclk high                                                             | 2T                     |     | ns   |

| IS6 | inval        | Data invalid time in slave mode, in this<br>period i2s_sclk should be high or low<br>but can not have positive edges |                        | //  | ns   |

#### Notes:

- (1) T = Cycle of i2s\_mclk

- (2) T1 = Cycle of i2s\_sclk

- 2. I2S TDM 传输协议

TDM 接口支持两种时序:

- 第一个声道(通道)起始与 FSYNC 上升沿对齐;

- 或者比 FSYNC 的上升沿 delay 一个 SCLK 时钟周期。

SCLK 时钟频率与采用率之间的关系如下(SCLK 与每帧声道个数、声道字长度、采样率有关):

Fsclk = channel\_num \* channel\_block\_length \* sample\_rate.

因 I2S 的标准接口是 TDM 传输标准的最简单形式, TDM 传输接口时序可参考 I2S 接口时序参数表。

# 4 机械特性

本章描述了 CFW32C7UL 芯片的机械特性。

#### **4.1** 封装材料

锡球成分如表 4-1 所示

表 4-1 封装材料

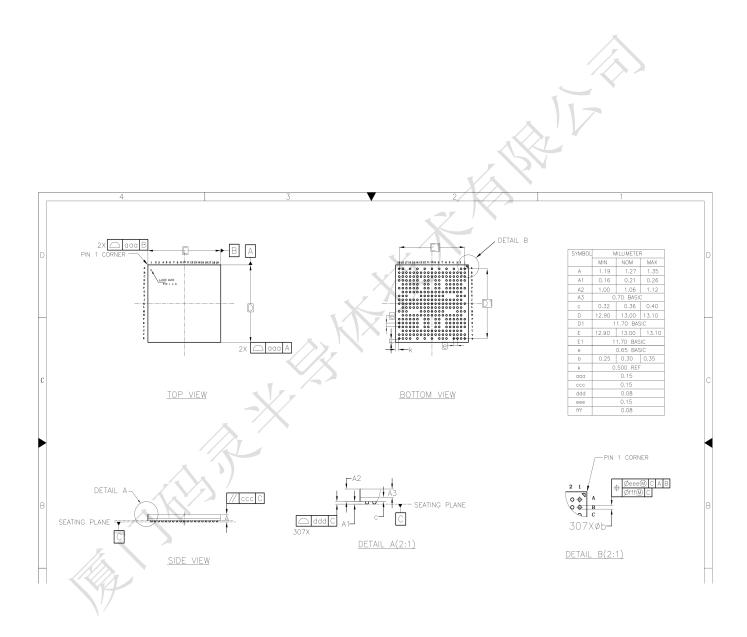

## 4.2 机械尺寸

#### 4.3 分类特征

| Profile Feature | Pb-Free Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | \rightarrow \right |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |